24小時聯(lián)系電話:18217114652、13661815404

中文

技術專題

旁路和去耦電容器放置準則

通常從電源的角度來看電源完整性問題,但是查看IC的輸出同樣重要。去耦電容和旁路電容旨在補償PDN上出現(xiàn)的功率波動,從而確保信號電平一致,并在IC的電源/接地引腳上看到恒定電壓。我們已經(jīng)匯編了一些重要的旁路和去耦電容器放置準則,以幫助您在下一個PCB中成功使用這些組件。

兩個相關的電源完整性問題

去耦電容器和旁路電容器用于解決兩個不同的電源完整性問題。盡管這些電源完整性問題是相關的,但它們以不同的方式表現(xiàn)出來。要注意的第一點是,術語“去耦電容器”和“旁路電容器”在用于電源完整性時是錯誤的。他們不會解耦或繞過任何東西。它們也不會將“噪音”傳遞給地面。它們只是隨時間推移進行充電和放電,以補償噪聲波動。這些術語將這些電容器的功能稱為電源完整性策略的一部分。

首先,考慮去耦電容器。一般說來,去耦電容器的目的是確保電源軌/接地層和接地層之間的電壓保持恒定,以抵抗低頻電源噪聲,PDN上的振鈴以及PDN上的任何其他電壓波動。當放置在電源和接地平面之間時,去耦電容器與這些平面并聯(lián),這會增加總的PDN電容。實際上,它們補償了平面間電容不足,并降低了PDN阻抗,從而使PDN電壓中的任何振鈴極小化。

現(xiàn)在考慮使用旁路電容器。它們還旨在在PDN和驅(qū)動IC內(nèi)保持恒定電壓,但是它們所補償?shù)碾妷涸谳敵鲆_和PCB接地層之間。盡管它們放置在電源引腳和IC上的接地之間,但它們執(zhí)行的功能是不同的,以防止接地反彈。當數(shù)字IC切換時,鍵合線,封裝和引腳中的寄生電感會導致驅(qū)動器輸出和地之間的電壓增加。旁路電容器輸出的電壓指向與地面反彈電壓相反的位置,理想情況下,使總電壓波動之和為零。

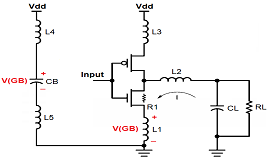

在以上模型中,存在一個閉環(huán),該閉環(huán)包括旁路電容器(CB)和IC封裝/接地連接上的雜散電感L1。請注意,在輸出引腳和接地層之間測量了接地反彈電壓 V(GB)。其余的電感都是寄生電容,會影響旁路電容器的響應時間以補償接地反彈。在理想模型中,旁路電容器看到的電壓將補償開關期間雜散電感器L1產(chǎn)生的接地反彈電壓。

旁路電容器放置準則

如果您看一下接地反彈的發(fā)生方式,那么應該在哪里放置旁路電容器應該很明顯。由于上述電路模型中的寄生電感,應將旁路電容器放置在盡可能靠近電源和接地引腳的位置,以極大程度地減小這些電感。這與您在許多應用筆記和組件數(shù)據(jù)手冊中找到的建議是一致的。

關于寄生電感,還有一個方面需要考慮,那就是如何將連接路由到IC。您應該通過過孔將電容器直接連接到接地層和電源層,而不是從電容器到IC引腳走一條短走線。確保符合此布置中的焊盤和走線間距要求。

為什么會這樣呢?原因是接地/電源平面布置(只要這些平面位于相鄰層中)將具有非常低的寄生電感。實際上,這是電路板上寄生電感的最低來源。如果您可以將旁路電容器放在電路板的底部,則可以實現(xiàn)更好的布置。

去耦電容器放置準則

確定PDN中所需的去耦電容器的尺寸后,需要將其放置在某處,以確保它可以補償輸入電壓波動。實際上,最好使用多個去耦電容器,因為它們將并聯(lián)排列,并且并聯(lián)排列將提供較低的有效串聯(lián)電感。

較早的準則會指出,您可以在板上的任何地方放置去耦電容器。但是,請注意這一點,因為這會增加去耦電容器和目標IC之間的寄生電感,從而增加PDN阻抗和對EMI的敏感性。相反,對于具有快速邊沿速率的IC,應將去耦電容器放置在靠近目標IC的位置。下圖顯示了IC附近的典型旁路和去耦電容器布置。這是高速電路的一種很好配置,因為對于所有信號路徑,電容器和IC之間的寄生電感非常低。

小心建模PDN阻抗

請記住,PDN阻抗決定了PDN上任何瞬態(tài)電壓振鈴的大小(在電源和地之間測得)。但是,旁路電容器也連接在電源和地之間,因此它們也是PDN的一部分!旁路和去耦電容器以及寄生電容和電感將共同決定PDN的阻抗譜,從而形成復雜的諧振和反諧振結構。

雖然您可以在線找到一些PDN優(yōu)化工具,但它們假定所有寄生電路元素均為零,這與實際情況不符。在電路模型中,如何布置去耦/旁路電容器(小到大或大到小)都無關緊要。在實際布局中,寄生因素很重要(如上所述),特別是對于高速/低電平IC。