24小時聯(lián)系電話:18217114652、13661815404

中文

技術(shù)專題

單端開關(guān)與差分信號

如今,當您談?wù)摳咚?/span>PCB設(shè)計時,幾乎在您看到的每個地方,產(chǎn)品所需的信號默認都是差分信號。但是,差分信號并不總是處于產(chǎn)品開發(fā)的最前沿。移動數(shù)據(jù)的原始方法是單端信令。而且,在某些情況下,它今天仍在使用。本文將描述單端和差分信號之間的區(qū)別,哪些邏輯系列具有單端信號,哪些邏輯具有差分信號,當前數(shù)據(jù)路徑需求,以及即將出現(xiàn)的變化。

單端交換特別地是指由驅(qū)動器和傳輸線組成的數(shù)據(jù)路徑,該傳輸器在平面上或在一對平面與一個或多個負載輸入之間傳播。您可以決定何時上升或下降沿經(jīng)過閾值電壓的任何時候發(fā)生邏輯狀態(tài)變化。

采用單端信號傳輸,如果要精確的時序,上升時間必須非常快。當您通過閾值電壓時,精確檢測邏輯狀態(tài)變化的能力取決于上升時間的快慢。

單端信令是發(fā)送邏輯信號的最便宜的方法,因為它對每個數(shù)據(jù)路徑只需要一根導線和一個信號引腳,所有數(shù)據(jù)路徑共享相同的“接地”平面。

BTL

CMOS

TTL

低壓CMOS

預(yù)期信用損失

GTL

左心室TTL

SSTL

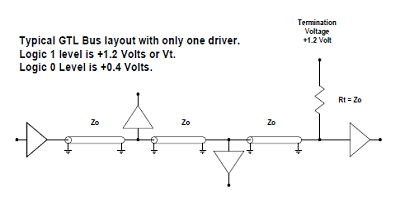

圖1描繪了BTL邏輯系列的單端數(shù)據(jù)路徑。當CMOS成為首選邏輯系列時,開發(fā)了BTL邏輯系列以替代ECL。它用于驅(qū)動大型數(shù)據(jù)總線。

圖1.單端信號數(shù)據(jù)路徑

對于所有上述邏輯系列,信號在兩端以及中間負載處均參考信號所經(jīng)過的平面。在大多數(shù)情況下,飛機是邏輯接地,但這不是強制性的。注入連接信號路徑元件的接地路徑的任何噪聲都會腐蝕出現(xiàn)在邏輯輸入端的邏輯電平。影響電流電平的常見噪聲類型是接地結(jié)構(gòu)中發(fā)生的DC和AC壓降,因為電流通過該路徑流回VDD。當邏輯電平從0切換到1并通過IC的電源線返回給邏輯線充電和放電所需的電流時,也會產(chǎn)生接地反彈。在大多數(shù)邏輯上,電源上的這種噪聲是EMI的主要來源。

特別是,發(fā)生的事情是,對傳輸線和邏輯器件的輸入的寄生電容進行充電和放電所需的電流成為Vdd上“紋波”的主要來源,而Vdd和接地反彈。注意:紋波是電源Vcc或Vdd軌上出現(xiàn)的電壓變化。這些變化可以通過電源本身或通過改變導致電源電壓下降的負載電流來產(chǎn)生。

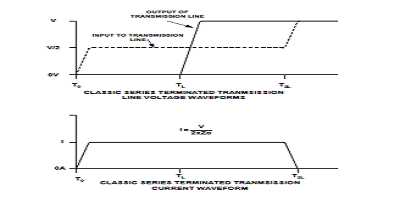

前述電流瞬變限制了可用于數(shù)據(jù)總線的實際寬度。圖2說明了當邏輯線路從邏輯0切換到邏輯1時,在串聯(lián)終端的傳輸線路中發(fā)生的電流。

圖2.串聯(lián)終端傳輸線的電壓和電流波形

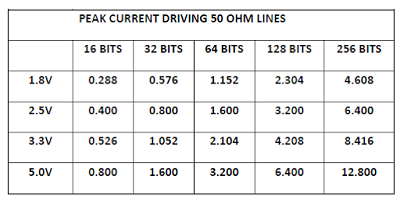

可以為任何邏輯系列計算圖2所示的電流。例如,如果邏輯系列為3.3V CMOS,則每條線的峰值電流約為33 mA。如果使用這種邏輯形式創(chuàng)建數(shù)據(jù)總線,則當所有位同時從0轉(zhuǎn)換到1時,總線所需的峰值電流為總線中位數(shù)的33 mA倍。表1列出了幾個邏輯系列的峰值電流(以安培為單位,在各種總線寬度下)。

表1.當所有線路從0變?yōu)?時,各種寬度數(shù)據(jù)總線的峰值電流

這些電流必須由電源系統(tǒng)提供。當邏輯線從邏輯0切換到邏輯1時,該電流必須流經(jīng)IC封裝引線的電感。當邏輯線從邏輯1切換到0時,傳輸線的寄生電容必須通過IC封裝的接地引線的電感放電。這就是兩種不想要的噪聲,即Vdd和接地反彈和紋波的產(chǎn)生位置。

這些噪聲源變得如此之大,以至于不再可能制造出具有足夠低電感的封裝以及功率子系統(tǒng)具有足夠高品質(zhì)的電容來容納此類噪聲。” “這就是導致使用差分信號的原因。”

歸根結(jié)底,單端開關(guān)的主要優(yōu)點是價格便宜。它的使用已被差分信號取代。我曾經(jīng)嘗試預(yù)測單端信令何時會消失,但是仍然可以在DDR內(nèi)存中找到,所以我不再做那些猜測了。

差分信號

差分信號是一個廣泛的話題,涉及許多因素。出于討論的目的,差分信令的主要好處是它具有應(yīng)付數(shù)據(jù)路徑兩端之間大量接地偏移的能力。注意:術(shù)語差分信令和串行信令可互換使用。

“使用差分信號時,您有兩條電線,它們的信號相等且相反。當兩個波形交叉時,數(shù)據(jù)位發(fā)生變化。因此,對于給定的數(shù)據(jù)速率,差分信號的邊緣不必像單端那樣快。”

最初,反對差分信令的情況就是代價。與單端信令相反,在差分信令中,每個數(shù)據(jù)路徑需要兩條線,兩個連接器引腳,兩個驅(qū)動器和兩個接收器。當數(shù)據(jù)速率相對較低并且信號路徑的兩端都在同一接地平面上時,就不需要承擔更高的差分信令成本。當單端數(shù)據(jù)路徑變得非常寬且信號的上升沿和下降沿變得非常快時,所產(chǎn)生的開關(guān)噪聲將使其難以達到噪聲目標。

表2列出了幾種類型的差分信令協(xié)議。所有這些都是為了應(yīng)付上述數(shù)據(jù)路徑兩端之間的接地偏移而創(chuàng)建的。

ECL

LVDS

雙相TTL時鐘樹

以太網(wǎng)鏈接

RS-422

HDMI

PCIExpress

Infinband

表2.幾種差分信令協(xié)議

“通常,我們將并行總線轉(zhuǎn)換為串行比特流。最初的PCI總線配置是137個帶時鐘的單端線。使用PCI Express,我可以用兩對差分來代替,每對都可以。這帶來了三個好處-我不需要超快速的上升時間,電源上沒有SSN,并且需要更少的電線來發(fā)送相同數(shù)量的數(shù)據(jù)。”

“使用差分信號,一方面,您必須獲取并行數(shù)據(jù)流,并將其轉(zhuǎn)換為串行(串行器)。另一方面,您必須將數(shù)據(jù)流從串行傳輸?shù)讲⑿校ń獯鳎?/span>” “執(zhí)行此操作所需的邏輯過去非常昂貴。結(jié)果,我們僅在遇到嚴重偏移問題時才使用差分信令。在當今擁有數(shù)十億個晶體管的邏輯的情況下,串行器和解串器基本上是免費的,我們正在將并行總線轉(zhuǎn)換為串行總線。使用現(xiàn)代串行鏈接,我們將時鐘嵌入到數(shù)據(jù)中,因此不再需要將時鐘與數(shù)據(jù)匹配的艱巨任務(wù)。您可以用這些東西構(gòu)建帶寬令人難以置信的系統(tǒng)。”