24小時聯系電話:18217114652、13661815404

中文

行業資訊

單線數據傳輸不同的方式

如果不需要高速,但需要靈活性,則在操作多個分散組件時,單線數據傳輸很有用。該方法通過減小尺寸和成本來減少電纜中的導體數量。它還可以提高系統可靠性。

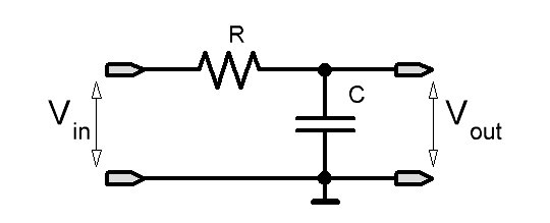

讓我們從經典的集成RC元素(圖1)及其屬性開始。集成RC元件可用于邏輯和數字電路中以更改脈沖長度,或更準確地說,生成或擴展脈沖持續時間,使用積分定律處理脈沖等。

1.這是典型的集成RC電路。

眾所周知,電容器電壓不能立即改變。其充電和放電時間取決于電容器C的容量和電阻R的電阻。可以使用根據以下公式計算的RC元件的時間常數來估算該時間:τ= RC。

如果將足夠長的脈沖發送到積分元件的輸入,則電容器將有時間完全充電和放電。但是,如果脈沖短,比時間常數τ短得多,則電容器C的電壓幾乎不變。

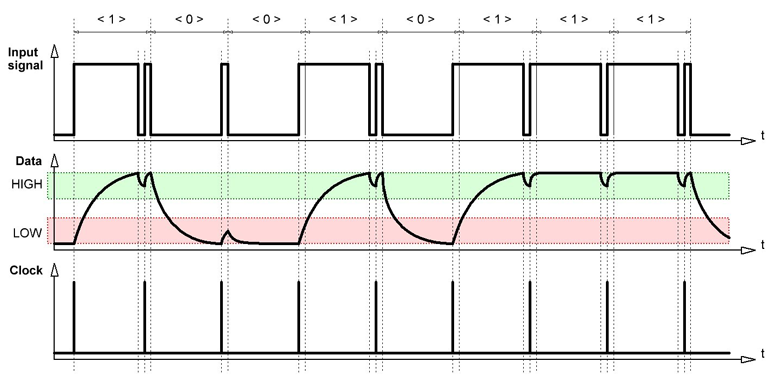

要傳輸串行代碼,我們需要有兩條數據線-數據和時鐘。如果以寬脈沖傳輸數據,而脈沖又有時間為RC元件的電容器充電,而時鐘以窄脈沖傳輸而無法通過積分元件,則可以將這兩條線合并為一條。因此,積分RC元件將用作信號接收器的分離器(圖2)。

2.顯示了為傳輸而生成的字節10010111(輸入信號)的示例。可以很容易地看出,要傳輸邏輯數據“一零”,必須生成一個相應的“高低”足夠寬的脈沖,并在最后加上一個短時鐘脈沖。

必須將時鐘信號放在RC元素之前,只有上升沿很重要,而數據信號則在RC元素之后。然后,如果正確生成位序列的傳輸信號,則可以解決該問題。圖2顯示了為傳輸而生成的字節10010111(輸入信號)的示例。

可以很容易地看出,為了傳輸邏輯數據“一/零”,必須生成一個相應的“高/低”足夠寬的脈沖,并在最后加上短時鐘脈沖(圖3)。

3.這顯示了一位“ HIGH , LOW”信號。每個都有一個尾隨時鐘脈沖

在這一點上,一個細心的讀者可能會提出一個邏輯問題:為什么可以直接使用經典延遲元件來完成,為什么要使用外部RC元件來分離數據和時鐘信號呢?展望未來,我們可以說使用外部RC元件使我們能夠大大減少接收器消耗的電流,因為我們停止使用延遲元件運行所需的內部振蕩器。

通過RC元件后收到的數據信號電壓必須在邏輯一個電壓的一定范圍內(圖2的綠色區域)。 時鐘信號電壓不應通過RC元件,也不應超出邏輯零電壓范圍(圖2的紅色區域)。 它們之間有一個模糊區域,完全可能存在錯誤狀態。因此,必須選擇電容器的容量和電阻器的電阻,以使所有“充電/放電”瞬態電壓值都不會落入該區域。這樣做的方法如下:

讓我們將圖1中的集成RC元件視為電阻R和電容器C的串聯連接。以下電路用于此類電路:

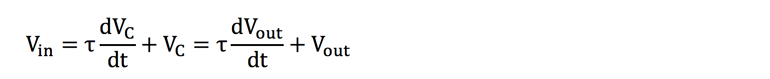

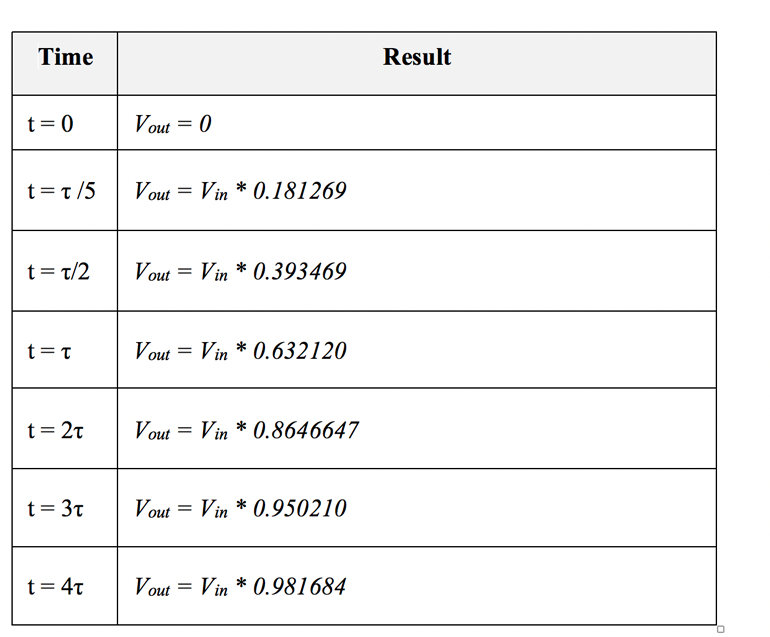

鑒于:

我們可以針對電容器電壓寫以下微分方程,實際上是積分元件的輸出電壓V C = V out:

這個微分方程的解是眾所周知的:

其中τ =時間常數。讓我們分析這個解決方案。在初始時間t = 0時,當輸入脈沖饋入積分元件時,輸出電壓為V out = 0,此后Vout 開始以與τ值成反比的速度增加,并達到以下值(圖4)。

4. RC元件后的數據信號電壓。

4. RC元件后的數據信號電壓。

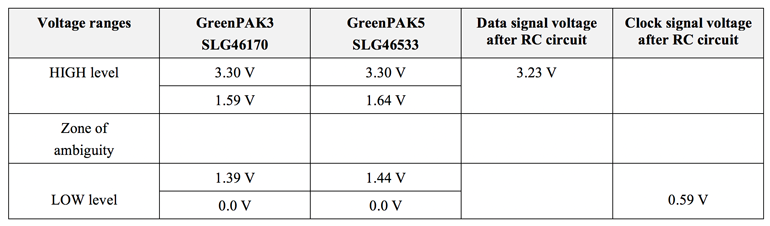

如下所述,發射機設計中比特序列傳輸信號的時間特性如圖3所示。接收器的結構中使用了具有以下參數的RC元件:R = 120Ω,С= 10 nF,τ= 1.2 μs (下面的圖14和15)。因此,可以計算出具有這樣持續時間的脈沖通過RC元件時獲得的電壓值。

持續時間為T1 = 5 μs的數據脈沖將適合t =4τ(更精確地說,t =4.17τ)的情況(圖4)。在V DD = 3.3 V的電壓下,RC元件之后的輸出電壓將為V out = 0.981684·3.3 V≈3.23 V;也就是我們需要的邏輯高電平。但是,短脈沖T2 = 240 ns必須由RC元件濾除。t =τ/ 5的情況對于持續時間T2 = 240 ns的時鐘脈沖有效(圖4)。

在V DD = 3.3 V的電壓下,RC元件之后的輸出電壓將為V out = 0.181269·3.3 V≈0.59 V,因此時鐘脈沖將不會通過RC元件。為了進行檢查,讓我們將獲得的合成信號電壓電平與特征邏輯“零/一”電壓電平進行比較。針對電源電壓為VDD 0 = 3.3 V的情況進行該比較(圖5)。

5.信號電壓電平。

因此,確保獲得的數據和時鐘信號的邏輯電平電壓值對應于所需的邏輯零/一電壓值,并且不會落入歧義區域。總結所有上述信息,選擇集成RC元素以分離數據和時鐘信號有兩個主要標準:

所選信號傳輸頻率下的信號持續時間T1應至少為RC元件時間常數τ的3倍,在我們的情況下為4.17倍:T1 =3τ

傳輸信號結束時短時鐘脈沖T2的持續時間至少應比RC元件的時間常數τ短4倍,在我們的情況下為5倍:T2 =τ/ 4

設計分析

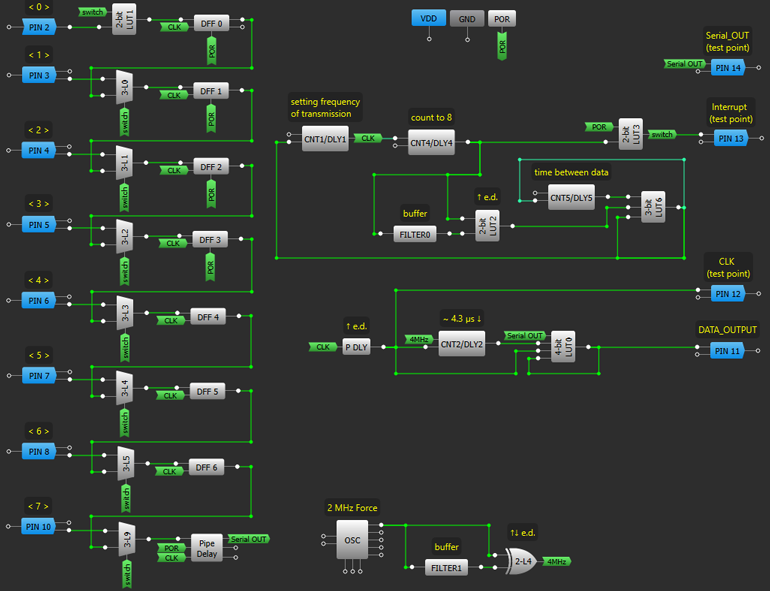

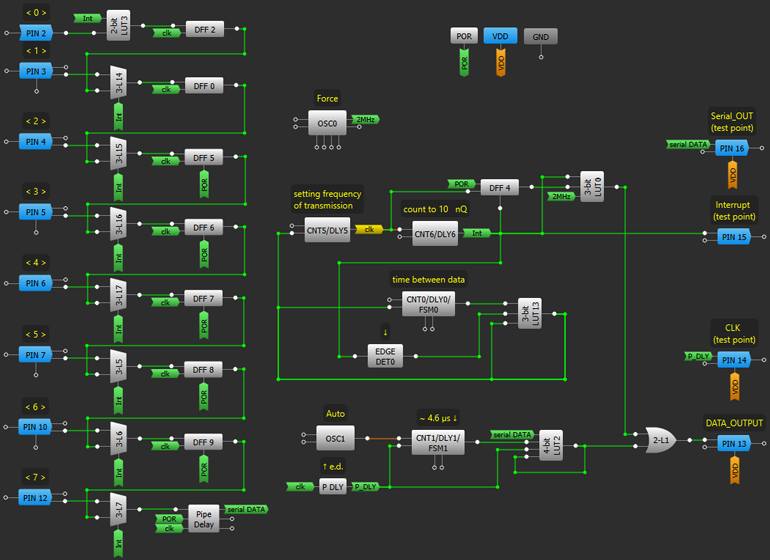

6.此“ Transmitter_170”設計實現了并行-串行轉換器。

Transmitter_170的設計(圖6)包含兩個主要組件:

基于2位LUT1、3位LUT0÷3位LUT5、3位LUT9,DFF0÷DFF6和流水線延遲的并行到串行轉換器

生成器根據CNT1,CNT4,DLY2,DLY5、2位LUT2、2位LUT3、3位LUT6、4位LUT0,FILTER0和P DLY生成必要的位序列傳輸信號

CNT1計數器定義了傳輸信號時間(如前所述,設置為?5 μs)。CNT4計數器形成八個這樣的時間段的數據包,并使用2位LUT3反相器控制2位LUT1、3位LUT0÷3位LUT5和3位LUT9多路復用器。當來自2位LUT3反相器輸出的內部“開關”信號為低電平時(圖7,“中斷”信號),則通過多路復用器記錄來自輸入PIN#2÷#8,#10的信息執行相應的觸發器。然后,當“ switch”(“中斷”信號)信號變高時,觸發器上的數據發生移位,并形成一個串行代碼(圖7,“ Serial_OUT”信號)。

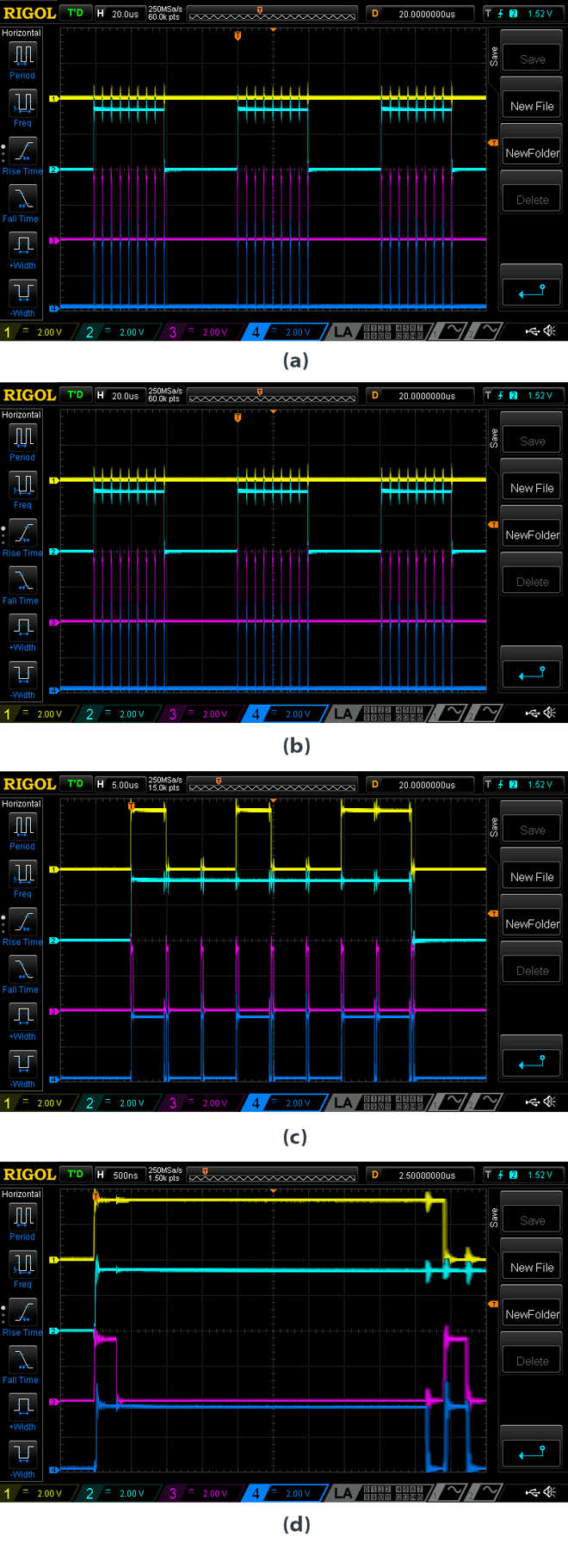

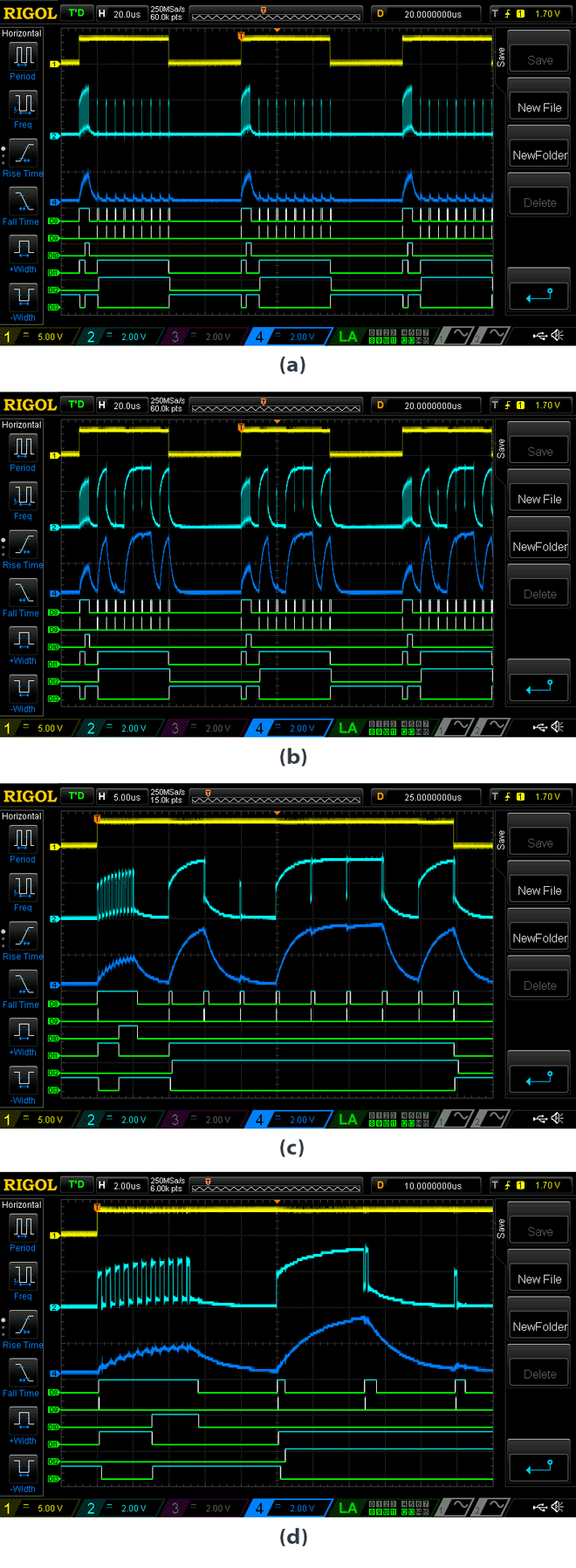

7.這些是“ Transmitter_170”傳輸的示例。通道1(黃色)是Serial_OUT,通道2(淺藍色)是中斷,通道3(品紅色)是時鐘,通道4(藍色)是DATA_OUTPUT。這些圖像顯示當輸入信號為00000000(a),輸入信號為10010011(b),輸入信號為10010011(c)時以及信號值較高的單個周期的縮放視圖(d)。

延遲元件DLY5以及3位LUT6元件和基于FILTER0和2位LUT2的上升沿檢測器允許改變所產生的數據分組之間的持續時間t2 (圖7b)。即,設置并行數據輸出的持續時間。當開關/中斷信號為低電平時,在接收轉換器的相應設計中會生成并行代碼。在我們的設計中,生成數據包的時間t1和生成時間t2大致相同。

來自最后一個Pipe Delay觸發器的輸出的生成的串行代碼被饋送到4位LUT0元素,在該元素中,使用延遲元素DLY2和上升沿檢測器P DLY,形成了所需的特定形式的輸出信號(圖7,“ DATA_OUTPUT”信號。由FILTER1和2位LUT4組成的上升沿和下降沿檢測器設計為使延遲元件DLY2的振蕩器時鐘頻率加倍,以提高最后一個的分辨率。

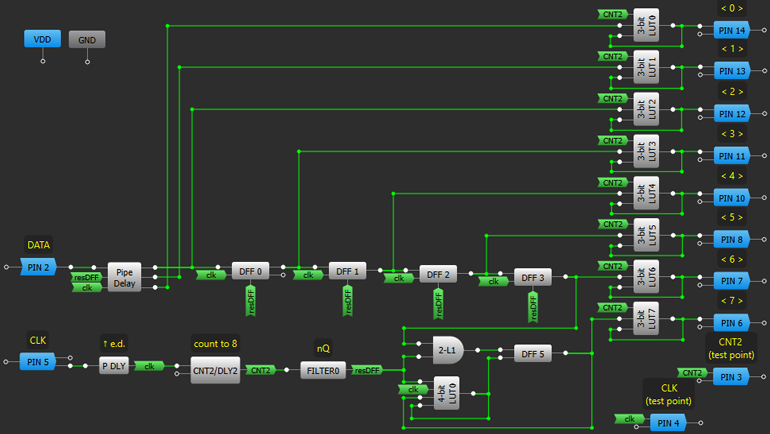

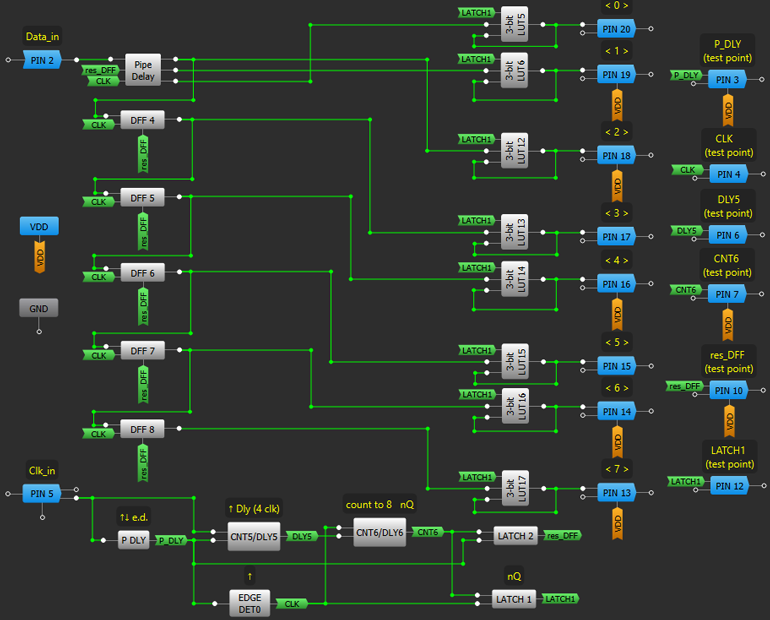

8.“ Receiver_170”設計實現了串行到并行轉換器。

Receiver_170的設計(圖8)執行將串行代碼轉換為并行代碼的相反功能。對于此操作,設計使用:

基于管道延遲(三個觸發器),DFF0÷DFF3和DFF5的八個觸發器鏈

基于3位LUT0÷3位LUT7的八個鎖存器,用于將并行代碼饋入輸出PIN

在上升沿檢測器P DLY上為觸發器鏈計時的電路;

CNT2計數器和FILTER0反相器上的鎖存器控制電路(3位LUT0÷3位LUT7元素)。

信號由外部RC元件分離后(圖14),來自輸入PIN#2 (圖9)的數據信號被饋送到觸發鏈的第一個觸發器。然后,我們使用P DLY檢測器僅選擇時鐘信號PIN#5的上升沿,并為觸發鏈和計數器CNT2形成時鐘信號。當內部CNT2信號為低電平(圖9,CNT2信號)時,串行代碼被解碼為觸發鏈上的并行代碼,在此觸發器由于來自FILTER0反相器輸出的高resDFF信號而處于觸發狀態。

9.這些是“ Receiver_170”接收的示例。通道1(黃色)是CNT2,通道2(淺藍色)是RC電路之前的外部信號,通道3(品紅色)是RC電路之后的外部信號,通道4(藍色)是CLK。這些圖像顯示當輸入信號為00000000(a),輸入信號為10010011(b),輸入信號為10010011(c)時以及信號值較高的單個周期的縮放視圖(d)。

當CNT2信號從低電平變為高電平時,表示每個觸發器當前狀態的信號將被饋入相應的鎖存器并存儲。同時,隨著resDFF信號從高電平變為低電平,解碼鏈的觸發器將重置為初始狀態。在“ CNT2”信號為高電平的時間期間,將鎖存器存儲的信號饋入相應的輸出PIN,這又對應于Transmitter_170設計中生成的數據包之間的時間t2。

DFF5觸發器沒有nRESET輸出。因此,它具有一個附加的復位邏輯電路,該電路基于AN-1029中所述的4位LUT0和2位LUT1元素。

仔細查看啟動Transmitter_170和Receiver_170設計的初始條件,一個明顯的缺點是。如果接收器比發送器晚開始運行,則串行代碼到并行的轉換可能不是從數據包的開頭開始,而是從中間開始。反過來,這將導致數據輸出過程發生變化。因此,為了確保發射器-接收器的正確操作,接收器必須與發射器同時開始工作。換句話說,它們必須具有公共電源(下面的圖14)。

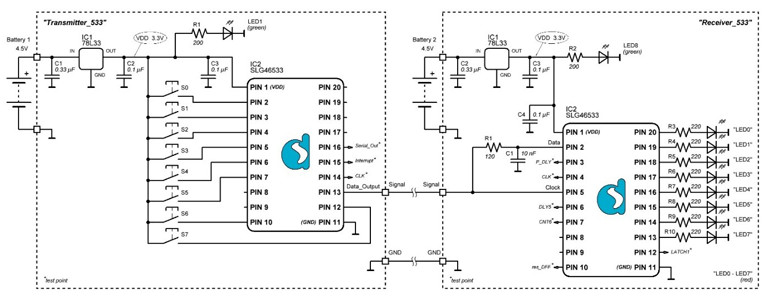

消除此缺陷的一種方法是,例如,在每個數據包的開頭發送服務輔助信號,以在開始轉換串行數據的過程之前重置接收機設計中的所有觸發器。這將確保數據轉換過程從程序包的開頭開始。這樣,我們將獲得一個可靠的數據傳輸系統,在該系統中,發送器和接收器可以擁有自己的電源,并可以隨時獨立于彼此開始運行。為了對此進行測試,創建了另一對Transmitter_533和Receiver_533 (圖15,進一步在下面)。

10.“ Transmitter_533”設計實現了并行-串行轉換器。

Transmitter_533的設計(圖10)也包含兩個主要組件:

基于2位LUT3、3位LUT14÷3位LUT17、3位LUT5÷3位LUT7,DFF2,DFF0,DFF5÷DFF9和流水線延遲的并行到串行轉換器

生成器根據CNT5,CNT6,DLY0,DLY1,DFF4、3位LUT0、3位LUT13,EDGE DET0,PDLY,4位LUT2和2位LUT1生成必要的位序列傳輸信號

此設計的操作原理與上一個沒有什么不同。同樣,CNT5計數器將傳輸信號時間定義為5 μs。但是,與先前的設計不同,CNT6計數器形成了10個此類時間段的數據包。即,除了設計用于發送數據的八個時段之外,還使用兩個另外的時段S1,S0來生成所需的服務信號(圖11c)。

11.這些是“ Transmitter_533”傳輸的示例。通道1(黃色)是Serial_OUT,通道2(淺藍色)是中斷,通道3(品紅色)是時鐘,通道4(藍色)是DATA_OUTPUT。圖像顯示輸入信號為00000000(a),輸入信號為10010011(b),輸入信號為10010011(c)以及服務信號的前兩個周期的縮放視圖(d)。

可能有很多方法來創建特殊服務信號,然后在接收器中對其進行檢測。我們選擇了第一個想到的:使用DFF4和3位LUT0,將服務信號的S1時間段填充為2 MHz的振蕩器頻率,并使用2位LUT1將其與主傳輸信號混合。留下S0時段而沒有任何改變(圖11d)。其原因將在接收機設計的描述中進行解釋。

像以前的發射機設計一樣,延遲元件DLY0以及3位LUT13元件和下降沿檢測器EDGE DET0使得可以更改生成的數據包之間的持續時間。與之前的情況一樣,根據DLY1、4位LUT2和P DLY創建所需的輸出信號特定形式(圖3)。由于數據包包含10個時間段,因此有必要在鏈中添加兩個觸發器以正確生成串行代碼。這是在管道延遲上完成的,其中OUT0設置為= 3。

因此,除數據字節外,在Transmitter_533的設計中還發送了兩個附加位S1和S0。S1位填充有振蕩器頻率為2 MHz的周期信號。

與先前的接收器一樣,Receiver_533 (圖12)的設計執行將串行碼解碼為并行碼的逆功能。另外,它在開始轉換串行數據的過程之前,會檢測到服務信號(由發送器生成)并重置所有觸發器。

12.“ Receiver_533”設計實現了串行到并行轉換器。

此功能通過DLY5延遲元件執行,其中PIN#5用作時鐘信號源。RC元素之前的Clock信號。檢測器P DLY的兩個邊沿對周期信號的響應(以2 MHz的頻率填充附加的S1位)類似于濾波器響應,這意味著可以為DLY5生成發射信號(圖13, P_DLY信號)。

DLY5是上升沿上的延遲元件,這就是為什么人們可以輕易地看到DLY5僅在附加的S1位到達時才起作用的原因(圖13,DLY5信號)。反過來,在開始并行到串行轉換之前,DLY5延遲元件將始終為CNT6計數器生成一個復位信號。這樣,CNT6計數器和兩個鎖存器(LATCH1和LATCH2)將生成必要的信號以重置解碼鏈中的觸發器(圖13,res_DFF信號)。另外,在并行數據輸出期間,用于在輸出中鎖存數據的信號鎖存3位LUT5、3位LUT6和3位LUT12÷3位LUT16 (圖13,LATCH1信號)。

13.這些是“ Receiver_533”接收的示例。通道1(黃色)是中斷,通道2(淺藍色)是RC電路之前的外部信號,通道4(藍色)是RC電路之后的外部信號。信號D8-D13(綠色)分別是P_DLY,CLK,DLY5,CNT6,res_DFF和LATCH1。圖像顯示輸入信號為00000000(a),輸入信號為10010011(b),輸入信號為10010011(c)以及服務信號的前兩個周期的縮放視圖(d)。

信號以其2 MHz的頻率填充了附加的S1位,滿足不通過RC元素的要求。但是,由于它在5 μs內多次重復,因此選擇了一位的持續時間,因此它設法將電容器充電到可以識別為邏輯電平的電壓電平。隨后,為使電容器放電至保證的邏輯零電平且不影響數據信號的位7,我們使用了第二個額外的S0位。

此外,為了提高系統的可靠性,用于觸發鏈和計數器CNT6的時鐘信號由上升沿檢測器EDGE DET0形成,該信號在P DLY元素之后獲取。繼而,這將防止在服務S1位的解碼期間產生寄生時鐘信號CLK (圖13,“ CLK”信號)。

其余元素執行與先前設計相同的功能。

電路分析

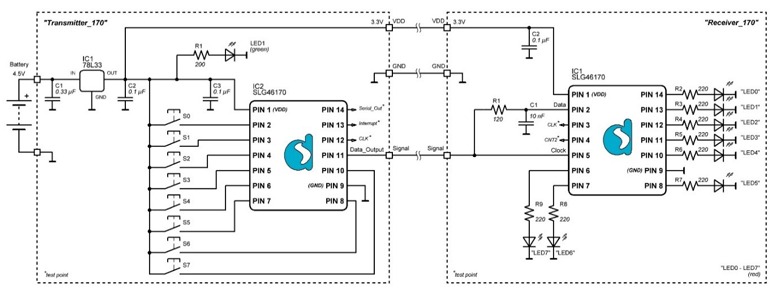

如前所述,為了演示所提出的數據傳輸原理的效率,我們創建了一對收發器設備。

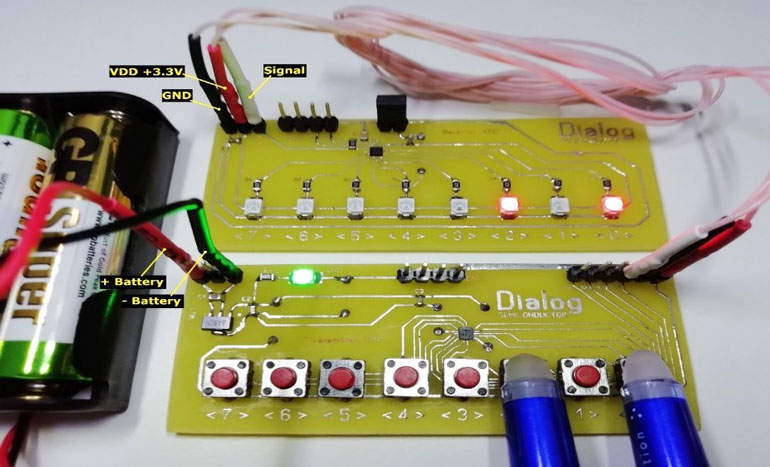

如上所述,Transmitter_170 – Receiver_170對(圖14)具有由使用的78L33線路穩定器確定的公共電源,其電源電壓為3.3V。在發射機電路中使用了八個按鈕S0÷S7來生成所需的傳輸信號。 。因此,接收器電路中的八個LED0÷LED7 LED用于可視化接收和解碼的信號。

14.這是典型的“ Transmitter_170 – Receiver_170”電路。

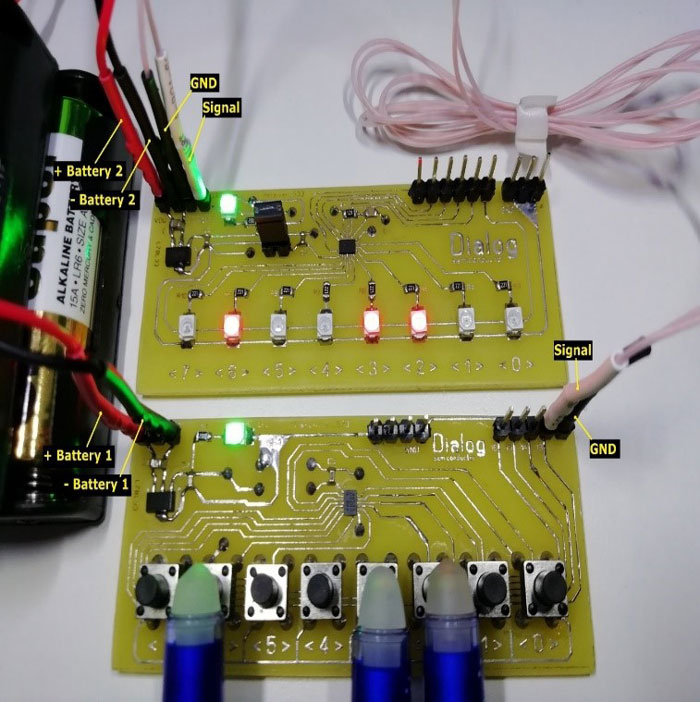

Transmitter_533-Receiver_533對(圖15)中的發送器和接收器具有獨立的電源節點,并且如上所述,它們代表一個獨立的數據接收-發送系統。像前面的電路一樣,按鈕S0÷S7可用于設置所需的傳輸信號。接收電路中的LED0÷LED7 LED可以監控結果。

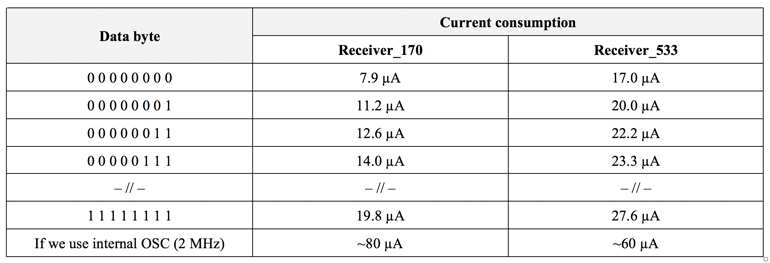

在不考慮LED消耗的電流的情況下,我們已經測量了在介紹的收發器對(Receiver_170的IC1電路和Receiver_533的IC2電路)工作期間芯片消耗的電流,以及它們的R1C1元件。事實證明,測得的電流值還取決于在串行信號字節中傳輸的邏輯電流的數量(這是由于RC元件電容器的充電電流所致)。為了比較,將測量結果匯總在圖16中。

16.基于數據值的電流消耗。

測得的電流值表明Receiver_533電路芯片消耗的電流略高于Receiver_170電路的電流。這是因為由于使用了附加的輔助服務位S1和S0,Receiver_533電路中的傳輸信號要長兩位。因此,可以總結出,帶有RC元件的芯片所消耗的電流遠小于帶有OSC 2 MHz振蕩器的芯片所消耗的電流。

圖17和圖18展示了基于上述工作原理的工作數據收發系統。

17.這是完整的“ Transmitter_170 – Receiver_170”系統(來自按鈕的輸入信號為00000101)。

18.這是一個完整的“ Transmitter_533 – Receiver_533”系統(來自按鈕的輸入信號為01001100)。